NSERC Accelerator Grants help to bring ECE research to Canadian Industry

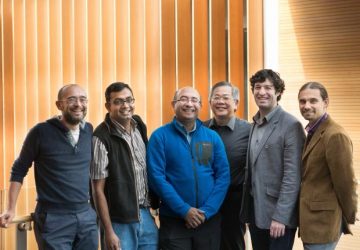

The National Science and Engineering Research Council supports the creativity and innovation of Canadian scientists through long-term funding known as Discovery Grants. From this select group of researchers, NSERC provides additional funding to scientists who show strong potential to become international leaders in their field. This funding, known as Discovery Accelerator Supplements, is a powerful resource. The grant brings $120,000 over three years to these outstanding scientists, so they can compete with the best in the world. The funding is used to expand research teams (students, postdoctoral fellows, technicians), for special equipment, and for other initiatives that will accelerate the progress of their research program. Six ECE researchers are currently supported by Accelerator Supplements and are using this funding to maximize the impact of their research for Canadian industries.

Fixing hardware glitches with software (without burdening programmers): Karthik Pattabiraman

As computer systems become smaller and faster, reliability becomes an important concern. One way of achieving high reliability is to design the system with many redundant components, so it can continue operating even if some of them fail. The trouble with this approach is that it consumes a lot of energy, an important concern for the next generation in computer systems such as smartphones and data centers. Computer engineers need new methods to ensure the reliability of future computer systems without relying on redundant hardware.

As computer systems become smaller and faster, reliability becomes an important concern. One way of achieving high reliability is to design the system with many redundant components, so it can continue operating even if some of them fail. The trouble with this approach is that it consumes a lot of energy, an important concern for the next generation in computer systems such as smartphones and data centers. Computer engineers need new methods to ensure the reliability of future computer systems without relying on redundant hardware.

Prof. Pattabiraman and his research team are experimenting with a new approach to reliability that compensates for hardware errors at the application software level, by building software that is resilient to hardware faults.

Few hardware errors actually make their way up the system stack to affect the application, and even the ones that do are not necessarily important to the application. It is much more efficient to protect software applications from (most) hardware faults, without adding significant amounts of redundancy. The main challenge however, is that it is difficult for programmers to make allowances for hardware faults at the software level, and to protect their applications without expending a huge amount of effort. Prof. Pattabiraman is working to completely automate the process of making applications error resilient without burdening the programmer.

The next generation of computer systems is predicted to occupy a substantial fraction of the total energy consumption costs by 2020. By helping to deliver reliability, higher performance and energy efficiency in the next generation of computer systems Prof. Pattabiraman’s novel approach to hardware errors will support the increase mobile computing, and support more energy-efficient internet data centers. As this research progresses, members of Prof. Pattabiraman’s research team are acquiring important skills to design and validate reliable computer systems; skills that are becoming more important as computer systems become more complex.

Graphing a deeper understanding: Matei Ripeanu

Graphs are the core data structure for problems in a wide set of domains from mining social networks, to genomics, to business and information analytics. In these domains, key to our ability to transform raw data into insights is the ability to process large graphs efficiently and at reasonable cost.

Graphs are the core data structure for problems in a wide set of domains from mining social networks, to genomics, to business and information analytics. In these domains, key to our ability to transform raw data into insights is the ability to process large graphs efficiently and at reasonable cost.

Imagine for example a power transmission grid. Redundant transmission paths between network nodes exist and power can be routed on a path based on the characteristics of the path and the cost of power. Estimating the impact of line failures and of possible corrective actions is critical to minimize blackouts and equipment damage. This analysis, however, is predicated on efficient support for large-scale graph processing.

While the insights we can gain from large-scale graphing are often crucial to our understanding of the complex systems in our global and highly integrated culture, the memory and computing power demands are so huge, these powerful tools for visualization are beyond the means of many researchers and business leaders.

Prof. Ripeanu and his research team are exploring three intertwined research directions:

- the feasibility of harnessing two recent advances in hardware, massively parallel (co)processors and solid state memories

- uncovering efficiencies in specific domains to enable harnessing them transparently to programmers through domain-specific runtimes.

- exploring avenues to simplify the development of graph analytics applications through domain-specific languages.

Prof. Ripeanu is focusing on two high-impact areas: social-networks and bioinformatics to develop this work. These domains offer challenging requirements in terms of problem scale, data diversity, and time-to-solution, and, at the same time, are witnessing the rapid development of an increasingly diverse set of complex algorithms.

Prof. Ripeanu experiments with computing infrastructure at NetSysLab where he and his team are developing Totem, a graph processing solution.

Meeting the growing demand for wireless access: Victor Leung

To meet the exponential growth of wireless traffic, mobile service providers are combining a number of technologies in heterogeneous networks that use a mixture of radio access technologies (RAT) like 3G/4G cellular and wireless local area networks (802.11n/ac). Although radio access technology is advancing, the system architecture has not kept up. New wireless system architectures need to be:

To meet the exponential growth of wireless traffic, mobile service providers are combining a number of technologies in heterogeneous networks that use a mixture of radio access technologies (RAT) like 3G/4G cellular and wireless local area networks (802.11n/ac). Although radio access technology is advancing, the system architecture has not kept up. New wireless system architectures need to be:

- scalable to provide increased capacity,

- programmable to support new functions and advanced RAT, and

- self-organized to enable “plug-and-play” deployment.

Prof. Leung and his research team are working to fill these gaps by developing of Smart Infrastructures for Radio Access as a Service (SIRAS). Prof. Leung’s team uses emerging cloud computing and virtualization techniques to create new approaches for wireless access networks.

Smart infrastructures for radio access extends the efficiency of cloud computing and the controllability and programmability of software-defined networks to wireless access networks, while exploiting recent advances in distributed antenna systems and software defined radios. Prof. Leung anticipates SIRAS replacing the current centralized cellular architecture with a distributed architecture that uses massively distributed antenna systems and autonomous small cells that collaborate. The network increases efficiency by using one of several, local RAT. Distributed interactions are coordinated by an extended control plane that uses software defined networking.

This distributed architecture would enable Radio Access as a Service by using cloud computing in an on-demand basis, in combination with local resources, to virtualize management and signal processing functions in a cost effective and scalable manner. SIRAS is one way to support the exponential growth in mobile services by increasing infrastructure capacities while guaranteeing quality of service with potential efficiencies in: cost, energy, complexity and latency.

To realize this vision, Prof. Leung and his research team in the Wireless Networks and Mobile Systems Laboratory are pursuing a new direction in wireless access networking. With postdoctoral fellows Liang Sun and Xiaofei Wang, Prof. Leung is developing new architecture, protocols and management algorithms that realize the potential benefits of SIRAS to improve future generation wireless access networks. Promising techniques that emerge from algorithm and protocol design will be evaluated under realistic conditions for proof-of-concept demonstrations and possible commercialization.

Keeping up with Moore’s Law: Lukas Chrostowski

Back in 1965, the co-founder of Intel, Dr. Gordon Moore, made a remarkably accurate prediction. He anticipated that computer chips would double in speed every two years, and he was right. Smaller and smaller transistors and more advanced chip architecture made Moore’s Law hold true from 1965 to 2012, but transistors appear to have reached a physical limit. As we bump up to that limit we are in danger of slowing down the entire pace of digital innovation.

Back in 1965, the co-founder of Intel, Dr. Gordon Moore, made a remarkably accurate prediction. He anticipated that computer chips would double in speed every two years, and he was right. Smaller and smaller transistors and more advanced chip architecture made Moore’s Law hold true from 1965 to 2012, but transistors appear to have reached a physical limit. As we bump up to that limit we are in danger of slowing down the entire pace of digital innovation.

Silicon photonics is an emerging field in optics, that enables CMOS electronics foundries to manufacture optical chips, known as photonic integrated circuits. Silicon photonics, using light to transmit data, is a way to continue to get faster data transfer in chips. Prof. Chrostowski’s research focuses on solving some of the major engineering problems associated with silicon photonics, with the aim of enabling the long-term success of this technology.

Prof. Chrostowski and his research team will be considering a number of stages of the manufacturing process to make design and fabrication more efficient. Design automation, expanding the optical component library and reducing the variability in manufacturing are some of the key issues Prof. Chrostowski is tackling with the support of the Accelerator Program. For example, PhD student Zeqin Lu is designing components that use dramatically less power, and are less sensitive to manufacturing variations; Zequin Lu has also narrated a video lab tour. Chrostowski’s research aims to provide Canadian companies with a state-of-the-art design platform and packaging service, for both small volume prototyping and large-scale manufacturing.

i-Guide-You, ultrasound guidance for spinal injections: Purang Abolmaesumi

Spinal needle injections are widely used for anesthetic purposes: for surgery, for the relief of back pain, and for epidurals in obstetrics. More than two million North Americans undergo these procedures each year. However, about 60,000 patients per year experience complications associated with inaccurate placement of the needle. These complications have three consequences: (1) an increase in pain, anxiety and the length of hospital stay, (2) a small number of patients suffering temporary or permanent neurologic deficit, and (3) the perceived risk inhibiting more widespread use of spinal needle injections.

Spinal needle injections are widely used for anesthetic purposes: for surgery, for the relief of back pain, and for epidurals in obstetrics. More than two million North Americans undergo these procedures each year. However, about 60,000 patients per year experience complications associated with inaccurate placement of the needle. These complications have three consequences: (1) an increase in pain, anxiety and the length of hospital stay, (2) a small number of patients suffering temporary or permanent neurologic deficit, and (3) the perceived risk inhibiting more widespread use of spinal needle injections.

To improve patient outcomes, several ultrasound-guided techniques have been proposed for more accurate placement of the needle. However, anesthesiologists find it difficult to see anatomical features and interpret the images, preventing ultrasound from becoming the standard-of-care.

Prof. Abolmaesumi and his research team are introducing intuitive guidance for intervention and diagnosis with enhanced ultrasound (i-Guide-U) technologies that augment computer models derived from other imaging techniques. I-Guide-U improves the quality of ultrasound images and enhance interpretations. For the first time, medical image registration and ultrasound tissue typing are being combined to dramatically improve ultrasound image formation quality based on the knowledge of the underlying anatomy.

Working from ECE’s Robotics and Control Lab Prof. Abolmaesumi is evaluating this method in the context of spinal needle injection for improved visibility of critical anatomical structures and targeting. With the support of the Accelerator Supplement Prof. Abolmaesumi is training two PhD, five MSc and five undergraduate students in leading-edge biomedical engineering research.

Building-Scale Energy Systems Incorporate a New DC/AC Balance: Martin Ordonez

The widespread use of direct current (DC) powered equipment (computers, telecoms, data centers, consumer electronics) has increased global electricity consumption by 27% over the past decade. In the US and Canada, DC power consumption produces 550 tons of harmful carbon emissions each year, and DC use is projected to increase even further with the addition of 20 million DC-powered electric vehicles (EV) by 2020, putting a significant burden on a century-old power infrastructure. Since power utilities deliver alternating current (AC) rather than DC, the conversion process used to power laptops and data centers is inefficient.

The widespread use of direct current (DC) powered equipment (computers, telecoms, data centers, consumer electronics) has increased global electricity consumption by 27% over the past decade. In the US and Canada, DC power consumption produces 550 tons of harmful carbon emissions each year, and DC use is projected to increase even further with the addition of 20 million DC-powered electric vehicles (EV) by 2020, putting a significant burden on a century-old power infrastructure. Since power utilities deliver alternating current (AC) rather than DC, the conversion process used to power laptops and data centers is inefficient.

Prof. Ordonez addresses the need for DC power by using a novel building-scale energy architecture. The short-term objective is to enable DC infrastructure within buildings to incorporate DC renewable generation and storage technologies (e.g. PV solar, batteries, and fuel cells) and supply the increasing amount of DC powered equipment directly (phasing out AC). This innovative program creates significant efficiency gains and cost reduction opportunities by using novel power conversion architecture and topologies. The elimination of conversion stages (DC/AC and AC/DC) can reduce emissions and maximize building efficiency. Consumers and utility providers will both benefit from advances in DC power storage and delivery.

From the end user perspective, the building’s power architecture will accommodate maximum DC power extraction (solar, batteries, fuel cells, etc.) and the next generation of high efficiency DC powering for lighting (LED), electric vehicle chargers, heating/cooling, etc. From the utility perspective, the building-scale energy system will have a perfect energy consumer profile. It will provide predictable/reliable energy use, enabling efficient peak shaving. These features will produce remarkable benefits for the power utility.

Prof. Ordonez and his research team are developing flexible, modular power converters. Their research program concentrates on definitive technical challenges associated with topological flexibility, scalability, power sharing, and control for the coordinated operation for DC infrastructure. Prof. Ordonez is also providing training in renewable power, and developing the intellectual capital Canadian industries need for research and development. Anticipating the high demand for engineers in renewable power, the program will deliver graduates with strong R&D skills for Canada.